# M69KB128AA

# 128 Mbit (8Mb x16) 1.8V Supply, Burst PSRAM

PRELIMINARY DATA

### Features summary

- SUPPLY VOLTAGE

- V<sub>CC</sub> = 1.7 to 1.95V core supply voltage

- $V_{CCQ}$  = 1.7 to 1.95V for I/O buffers

- USER-SELECTABLE OPERATING MODES

- Asynchronous Modes: Random Read, and Write, Page Read

- Synchronous Modes: NOR-Flash, Full Synchronous (Burst Read and Write)

- ASYNCHRONOUS RANDOM READ

- Access Times: 70ns, 85ns

- ASYNCHRONOUS PAGE READ

- Page Size: 4, 8 or 16 Words

- Subsequent Read Within Page: 20ns

- BURST READ

- Fixed Length (4, 8, 16 or 32 Words) or Continuous

- Maximum Clock Frequency: 66, 80, 104MHz

- Output delay: 7ns at 104MHz

- LOW POWER CONSUMPTION

- Active Current: < 25mA</li>

- Standby Current: 200µA

- Deep Power-Down Current: 10µA

- LOW POWER FEATURES

- Partial Array Self Refresh (PASR)

- Deep Power-Down (DPD) Mode

- OPERATING TEMPERATURE

- − −30°C to +85°C

#### M69KB128AA IS ONLY AVAILABLE AS PART OF A MULTIPLE MEMORY PRODUCT

January 2006

# Contents

| 1 | Sum  | mary description7                                   |

|---|------|-----------------------------------------------------|

| 2 | Sign | al descriptions                                     |

|   | 2.1  | Address Inputs (A0-A22)                             |

|   | 2.2  | Data Inputs/Outputs (DQ8-DQ15) 10                   |

|   | 2.3  | Data Inputs/Outputs (DQ0-DQ7)                       |

|   | 2.4  | Chip Enable (E)                                     |

|   | 2.5  | Output Enable (G)                                   |

|   | 2.6  | Write Enable (W)                                    |

|   | 2.7  | Upper Byte Enable (UB) 10                           |

|   | 2.8  | Lower Byte Enable (LB) 11                           |

|   | 2.9  | Clock Input (K) 11                                  |

|   | 2.10 | Configuration Register Enable (CR) 11               |

|   | 2.11 | Latch Enable (L)                                    |

|   | 2.12 | Wait (WAIT)                                         |

|   | 2.13 | V <sub>CC</sub> Supply Voltage                      |

|   | 2.14 | V <sub>CCQ</sub> Supply Voltage 12                  |

|   | 2.15 | V <sub>SS</sub> Ground                              |

|   | 2.16 | V <sub>SSQ</sub> Ground                             |

| 3 | Powe | ər-up                                               |

| 4 | Low- | power modes                                         |

|   | 4.1  | Standby                                             |

|   | 4.2  | Deep Power-Down                                     |

|   | 4.3  | Partial Array Self Refresh 14                       |

| 5 | Stan | dard asynchronous operating modes15                 |

|   | 5.1  | Asynchronous Read and Write modes 15                |

|   | 5.2  | Asynchronous Page Read mode 15                      |

|   | 5.3  | Configuration Registers Asynchronous Read and Write |

| 6  | Syncl  | hronou  | is operating modes                                     | 18   |

|----|--------|---------|--------------------------------------------------------|------|

|    | 6.1    | NOR-F   | Flash Synchronous mode                                 | 18   |

|    | 6.2    | Full Sy | nchronous mode                                         | 19   |

|    | 6.3    | Synchi  | ronous Burst Read and Write                            | 19   |

|    |        | 6.3.1   | Variable Latency                                       |      |

|    |        | 6.3.2   | Fixed Latency                                          | . 20 |

|    |        | 6.3.3   | Row Boundary crossing                                  | . 20 |

|    | 6.4    | Synchi  | ronous Burst Read Interrupt                            | 21   |

|    | 6.5    | Synchi  | ronous Burst Write Interrupt                           | 21   |

|    | 6.6    | Synchi  | ronous Burst Read and Write Suspend                    | 21   |

| 7  | Confi  | guratio | on registers                                           | 27   |

|    | 7.1    | Progra  | mming the Registers by the CR controlled method        | 27   |

|    |        | 7.1.1   | Read Configuration Register                            | . 27 |

|    |        | 7.1.2   | Program Configuration Register                         | . 27 |

|    | 7.2    | Progra  | mming and Reading the Registers by the software method | 28   |

|    | 7.3    | Bus Co  | onfiguration Register                                  | 30   |

|    |        | 7.3.1   | Operating Mode Bit (BCR15)                             | . 30 |

|    |        | 7.3.2   | Latency Type (BCR14)                                   | . 30 |

|    |        | 7.3.3   | Latency Counter Bits (BCR13-BCR11)                     | . 30 |

|    |        | 7.3.4   | WAIT Polarity Bit (BCR10)                              | . 30 |

|    |        | 7.3.5   | WAIT Configuration Bit (BCR8)                          |      |

|    |        | 7.3.6   | Driver Strength Bits (BCR5-BCR4)                       |      |

|    |        | 7.3.7   | Burst Wrap Bit (BCR3)                                  |      |

|    |        | 7.3.8   | Burst Length Bits (BCR2-BCR0)                          | . 31 |

|    | 7.4    | Refres  | h Configuration Register                               |      |

|    |        | 7.4.1   | Page Mode Operation Bit (RCR7)                         |      |

|    |        | 7.4.2   | Deep Power-Down Bit (RCR4)                             |      |

|    |        | 7.4.3   | Partial Array Refresh Bits (RCR2-RCR0)                 |      |

|    | 7.5    | Device  | ID Register                                            | 37   |

| 8  | Maxin  | num R   | ating                                                  | 38   |

| 9  | DC ar  | nd AC I | parameters                                             | 39   |

| 10 | Part N | lumbe   | ring                                                   | 66   |

|    |        |         |                                                        |      |

| 11 | Revision history | <b>;</b> 7 |

|----|------------------|------------|

|----|------------------|------------|

# List of tables

| Table 1.  | Signal Names                                               | 8  |

|-----------|------------------------------------------------------------|----|

| Table 2.  | Page Mode Characteristics.                                 | 16 |

| Table 3.  | Standard Asynchronous Operating Modes                      | 17 |

| Table 4.  | Operating Frequency versus Latency                         | 22 |

| Table 5.  | Asynchronous Write Operations (NOR-Flash Synchronous mode) | 22 |

| Table 6.  | Synchronous Read Operations (NOR-Flash Synchronous mode)   | 23 |

| Table 7.  | Full Synchronous mode                                      | 24 |

| Table 8.  | Register Selection.                                        | 28 |

| Table 9.  | Bus Configuration Register Definition                      | 32 |

| Table 10. | Burst Type Definition                                      | 33 |

| Table 11. | Refresh Configuration Register Definition                  | 36 |

| Table 12. | Device ID Register Definition                              | 37 |

| Table 13. | Absolute Maximum Ratings                                   | 38 |

| Table 14. | Operating and AC Measurement Conditions                    | 39 |

| Table 15. | Capacitance                                                | 40 |

| Table 16. | DC Characteristics                                         | 41 |

| Table 17. | Asynchronous Read AC Characteristics                       | 42 |

| Table 18. | Asynchronous Page Read AC Characteristics                  | 43 |

| Table 19. | Asynchronous Write AC Characteristics                      | 46 |

| Table 20. | Clock Related AC Timings                                   | 52 |

| Table 21. | Synchronous Burst Read AC Characteristics                  | 52 |

| Table 22. | Synchronous Burst Write AC Characteristics                 | 59 |

| Table 23. | Power-Up and Deep Power-Down AC Characteristics            | 65 |

| Table 24. | Ordering Information Scheme                                | 66 |

| Table 25. | Document Revision History                                  | 67 |

# List of figures

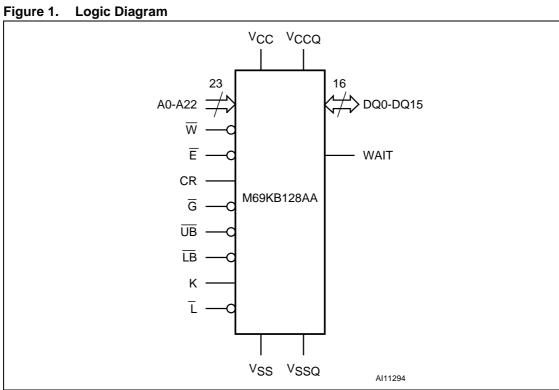

| Figure 1.  | Logic Diagram.                                                                | . 8 |

|------------|-------------------------------------------------------------------------------|-----|

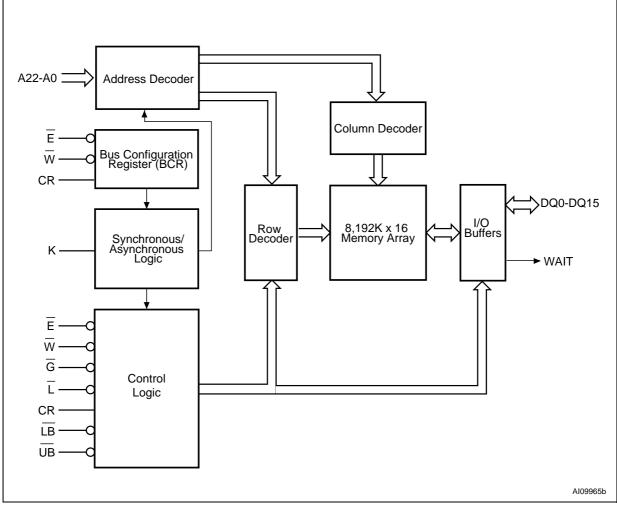

| Figure 2.  | Block Diagram                                                                 | . 9 |

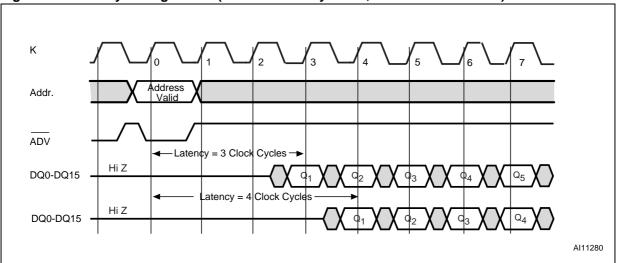

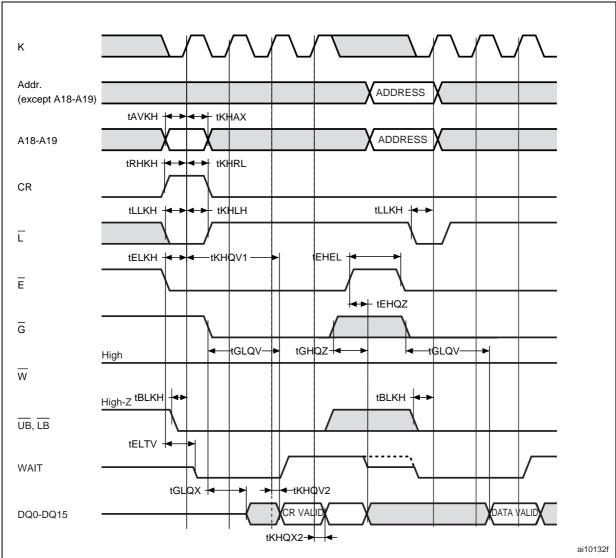

| Figure 3.  | Latency Configuration (Variable Latency mode, no Refresh collision)           | 25  |

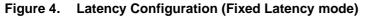

| Figure 4.  | Latency Configuration (Fixed Latency mode)                                    | 25  |

| Figure 5.  | Switching from Asynchronous to Synchronous Write operation                    | 26  |

| Figure 6.  | Refresh Collision during Synchronous Read Operation in Variable Latency mode  | 26  |

| Figure 7.  | Set Configuration Register (Software Method)                                  |     |

| Figure 8.  | Read Configuration Register (Software Method)                                 | 29  |

| Figure 9.  | WAIT Configuration Example                                                    | 34  |

| Figure 10. | WAIT Polarity                                                                 |     |

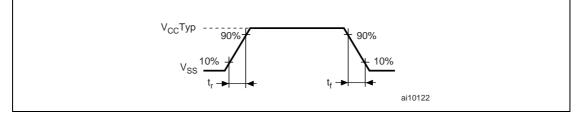

| Figure 11. | AC Measurement I/O Waveform                                                   |     |

| Figure 12. | AC Input Transitions                                                          |     |

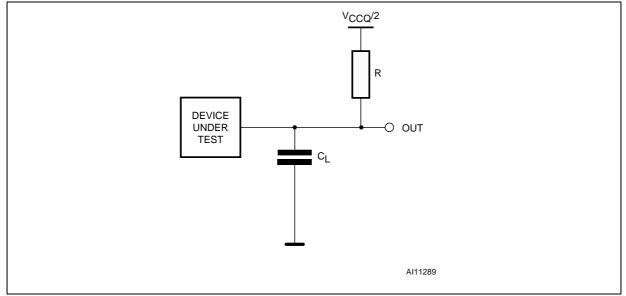

| Figure 13. | AC Measurement Load Circuit                                                   |     |

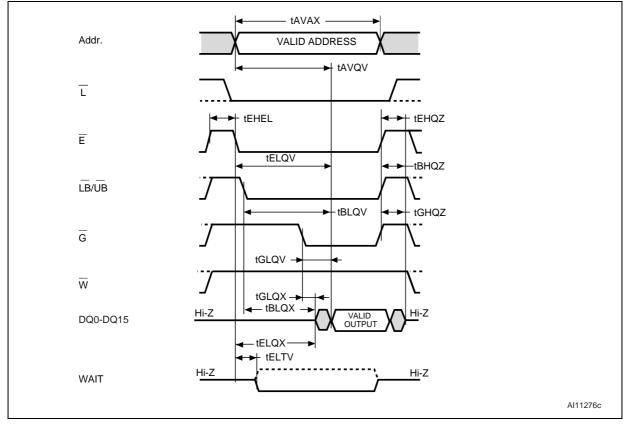

| Figure 14. | Asynchronous Random Read AC Waveforms                                         | 43  |

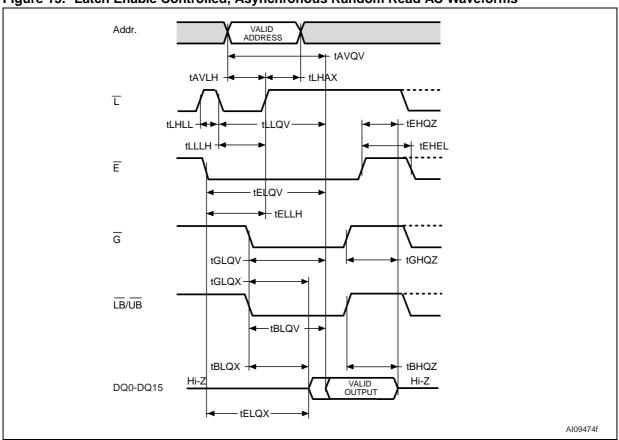

| Figure 15. | Latch Enable Controlled, Asynchronous Random Read AC Waveforms                |     |

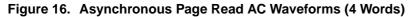

| Figure 16. | Asynchronous Page Read AC Waveforms (4 Words)                                 |     |

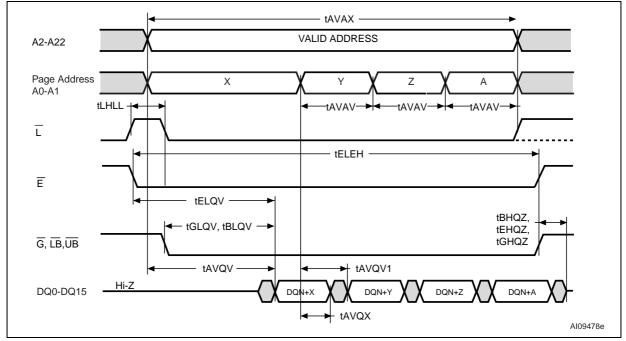

| Figure 17. | CR Controlled Configuration Register Read Followed by Read, Asynchronous Mode | 45  |

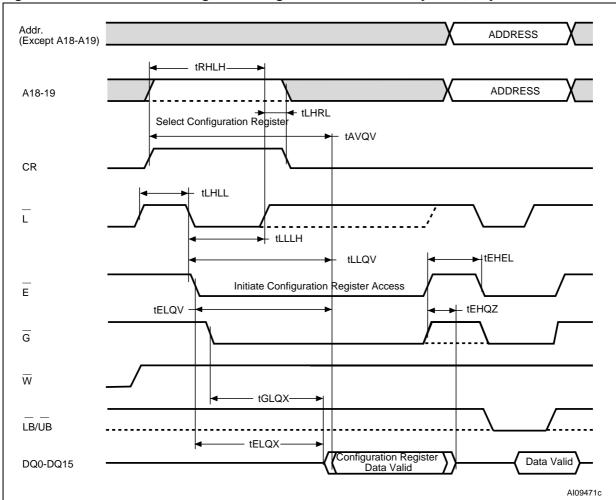

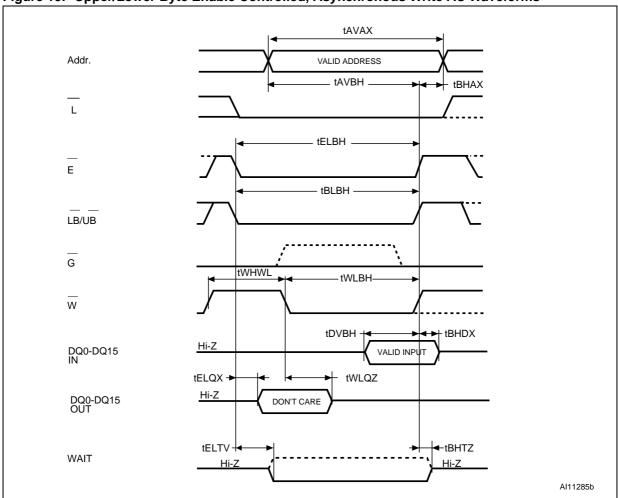

| Figure 18. | Chip Enable Controlled, Asynchronous Write AC Waveforms                       |     |

| Figure 19. | Upper/Lower Byte Enable Controlled, Asynchronous Write AC Waveforms           |     |

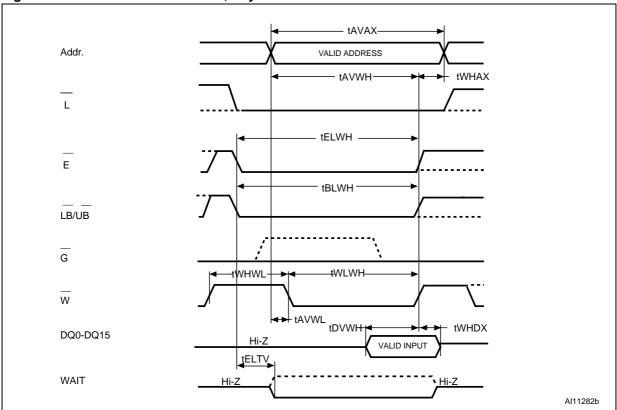

| Figure 20. | Write Enable Controlled, Asynchronous Write AC Waveforms.                     |     |

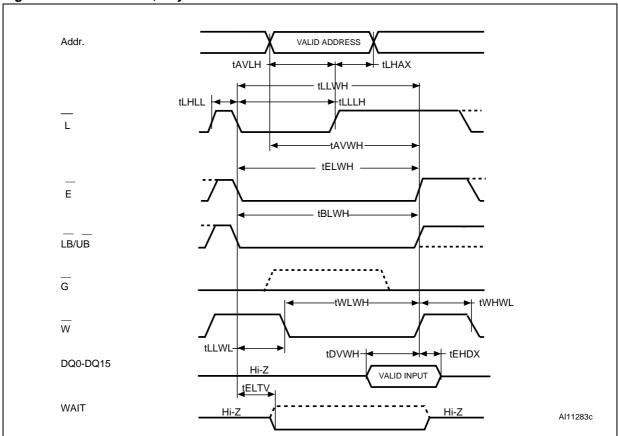

| Figure 21. | L Controlled, Asynchronous Write AC Waveforms                                 |     |

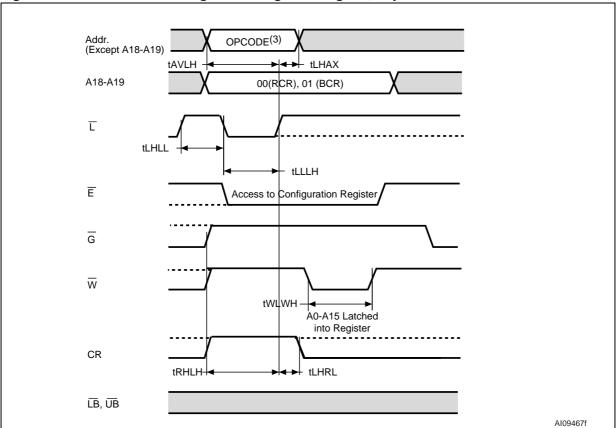

| Figure 22. | CR Controlled Configuration Register Program, Asynchronous Mode               |     |

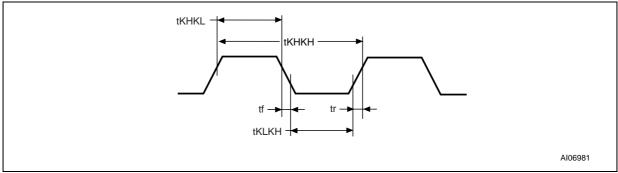

| Figure 23. | Clock input AC Waveform.                                                      |     |

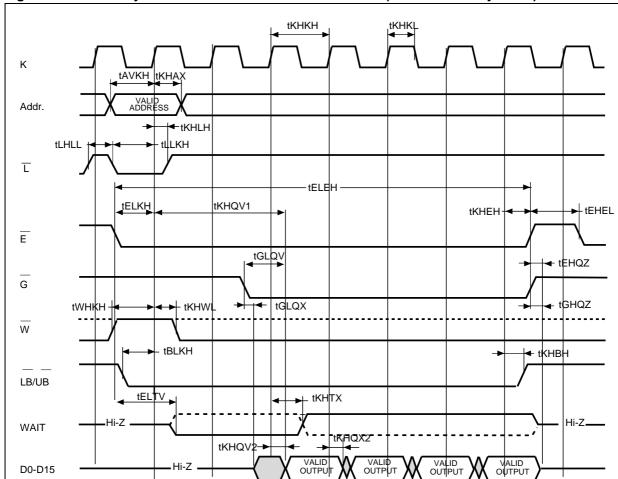

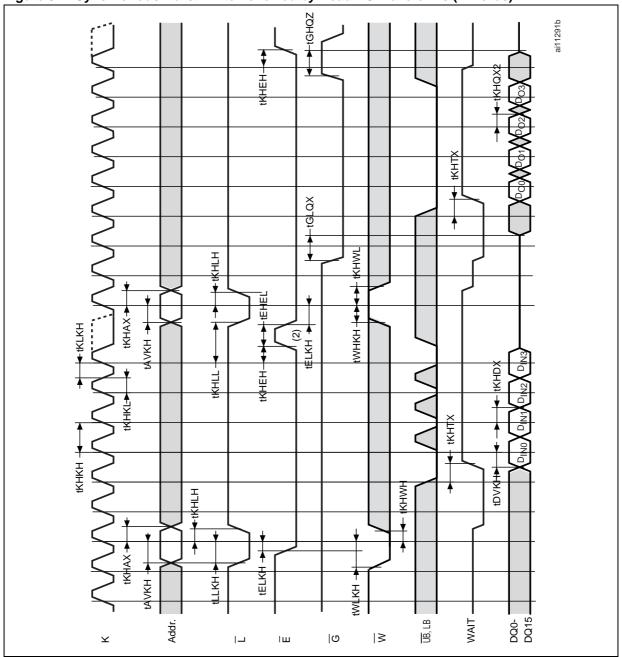

| Figure 24. | 4-Word Synchronous Burst Read AC Waveforms (Variable Latency Mode)            |     |

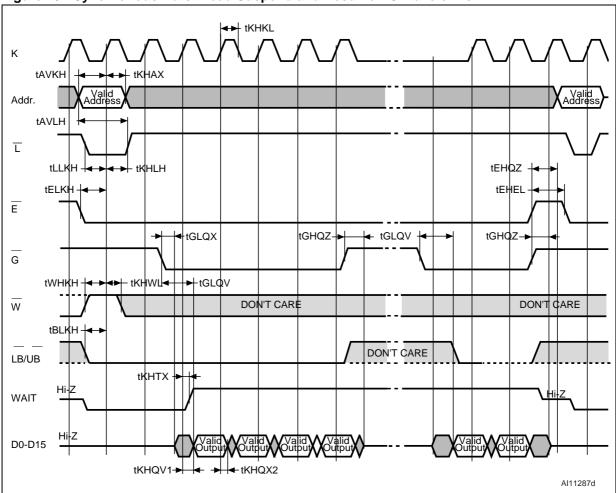

| Figure 25. | Synchronous Burst Read Suspend and Resume AC Waveforms                        |     |

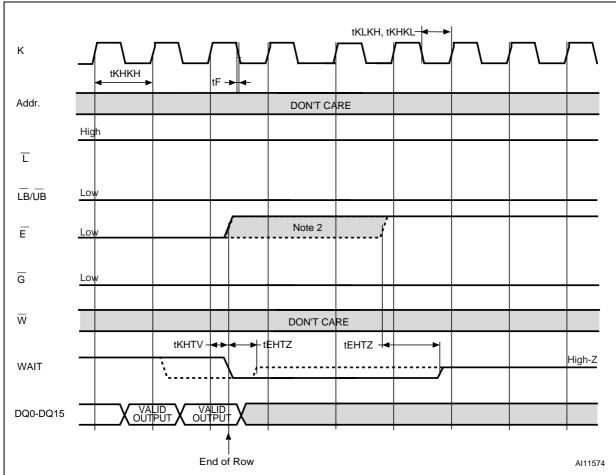

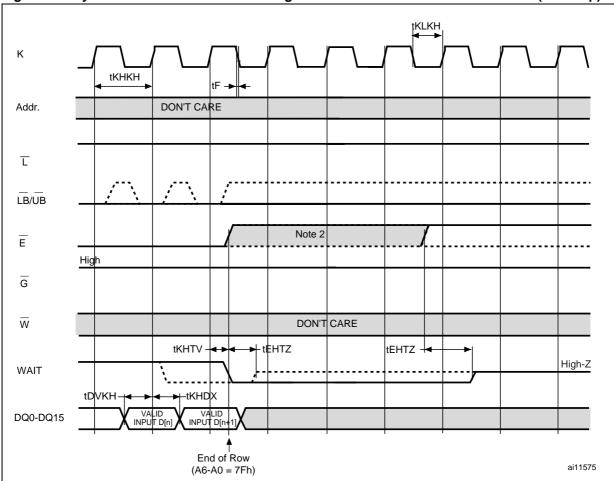

| Figure 26. | Synchronous Burst Read Showing End-of-Row Condition AC Waveforms (No Wrap)    |     |

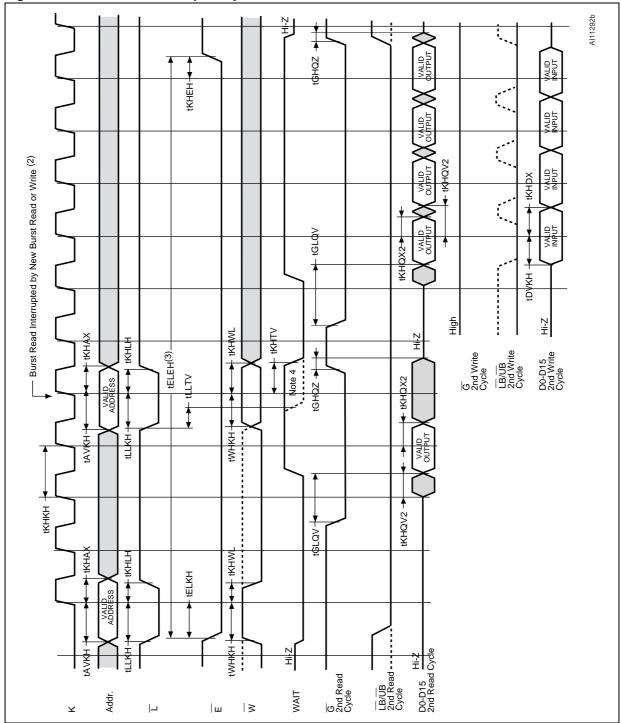

| Figure 27. | Burst Read Interrupted by Burst Read or Write AC Waveforms                    |     |

| Figure 28. | CR Controlled Configuration Register Read Followed by Read, Synchronous Mode  |     |

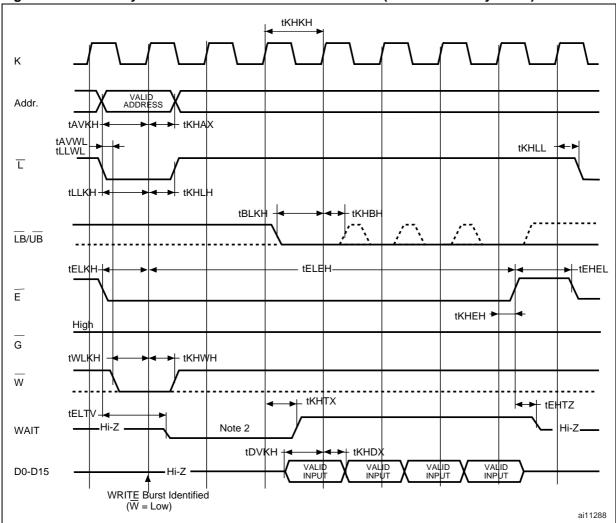

| Figure 29. | 4-Word Synchronous Burst Write AC Waveforms (Variable Latency Mode)           | 60  |

| Figure 30. | Synchronous Burst Write Showing End-of-Row Condition AC Waveforms (No Wrap)   |     |

| Figure 31. | Synchronous Burst Write Followed by Read AC Waveforms (4 Words)               | 62  |

| Figure 32. | Burst Write Interrupted by Burst Write or Read AC Waveforms                   | 63  |

| Figure 33. | CR Controlled Configuration Register Program, Synchronous Mode                | 64  |

| Figure 34. | Power-Up AC Waveforms.                                                        |     |

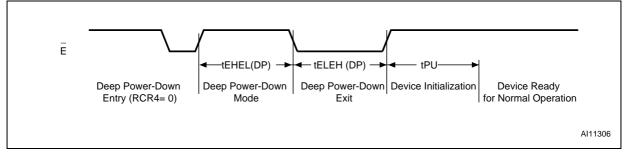

| Figure 35. | Deep Power-Down Entry and Exit AC Waveforms                                   | 65  |

# **1** Summary description

The M69KB128AA is a 128 Mbit (134,217,728 bit) PSRAM, organized as 8,388,608 Words by 16 bits. It uses a high-speed CMOS DRAM technology implemented using a one transistor-percell topology that achieves bigger array sizes. It provides a high-density solution for low-power handheld applications.

The M69KB128AA is supplied by a 1.7 to 1.95V supply voltage range.

The PSRAM interface supports various operating modes: Asynchronous Random Read and Write, Asynchronous Page Read and Synchronous mode that increases read/write speed.

In Asynchronous Random Read mode, the M69KB128AA is compatible with low power SRAMs. In Asynchronous Page mode the device has much shorter access times within the page that make it is compatible with the industry standard PSRAMs.

Two types of Synchronous modes are available:

- Flash-NOR: the device operates in Synchronous mode for read operations and Asynchronous mode for write operations.

- Full Synchronous: the device supports Synchronous transfers for both read and write operations.

The M69KB128AA features three configuration registers:

- Two user-programmable registers used to define the device operation: the Bus Configuration Register (BCR) and the Refresh Configuration Register (RCR).

- A read-only Device ID Register (DIDR) containing device identification.

The Bus Configuration Register (BCR) indicates how the device interacts with the system memory bus. The Refresh Configuration Register (RCR) is used to control how the memory array refresh is performed. At Power-Up, these registers are automatically loaded with default settings and can be updated any time during normal operation.

PSRAMs are based on the DRAM technology, but have a transparent internal self-refresh mechanism that requires no additional support from the system memory microcontroller.

To minimize the value of the Standby current during self-refresh operations, the M69KB128AA includes two system-accessible mechanisms configured via the Refresh Configuration Register (RCR):

- The Partial Array Self Refresh (PASR) performs a limited refresh of the part of the PSRAM array that contains essential data.

- The Deep Power-Down (DPD) mode completely halts the refresh operation. It is used when no essential data is being held in the device.

|                      | G     —     М69КВ128АА       UB     —     С       LB     —     С       K     — |

|----------------------|--------------------------------------------------------------------------------|

|                      | V <sub>SS</sub> V <sub>SSQ Al11294</sub>                                       |

| Table 1. Signal Name | s                                                                              |

| A0-A22               | Address Inputs                                                                 |

| DQ0-DQ15             | Data Inputs/Outputs                                                            |

| Ē                    | Chip Enable Input                                                              |

| CR                   | Configuration Register Enable Input                                            |

| G                    | Output Enable Input                                                            |

| Configuration Register Enable Input |

|-------------------------------------|

| Output Enable Input                 |

| Write Enable Input                  |

| Upper Byte Enable Input             |

| Lower Byte Enable Input             |

| Clock Input                         |

| Latch Enable Input                  |

| Wait Output                         |

| Core Supply Voltage                 |

| Input/Output Buffers Supply Voltage |

| Ground                              |

| Input/Output Buffers Ground         |

|                                     |

#### Figure 2. Block Diagram

1. This functional block diagram illustrates simplified device operation.

# 2 Signal descriptions

The signals are summarized in Figure 1: Logic Diagram, and Table 1: Signal Names.

#### 2.1 Address Inputs (A0-A22)

The Address Inputs select the cells in the memory array to access during read and write operations.

#### 2.2 Data Inputs/Outputs (DQ8-DQ15)

The Upper Byte Data Inputs/Outputs carry the data to or from the upper part of the selected address during a write or read operation, when Upper Byte Enable  $(\overline{\text{UB}})$  is driven Low. When disabled, the Data Inputs/Outputs are high impedance.

### 2.3 Data Inputs/Outputs (DQ0-DQ7)

The Lower Byte Data Inputs/Outputs carry the data to or from the lower part of the selected address during a write or read operation, when Lower Byte Enable ( $\overline{\text{LB}}$ ) is driven Low. When disabled, the Data Inputs/Outputs are high impedance.

### 2.4 Chip Enable ( $\overline{E}$ )

Chip Enable,  $\overline{E}$ , activates the device when driven Low (asserted). When deasserted (V<sub>IH</sub>), the device is disabled and goes automatically in low-power Standby mode or Deep Power-Down mode, according to the RCR settings.

### 2.5 Output Enable ( $\overline{G}$ )

When held Low,  $V_{IL}$ , the Output Enable,  $\overline{G}$ , enables the Bus Read operations of the memory.

#### 2.6 Write Enable ( $\overline{W}$ )

Write Enable,  $\overline{W}$ , controls the Bus Write operation of the memory. When asserted (V<sub>IL</sub>), the device is in write mode and write operations can be performed either to the configuration registers or to the memory array.

# 2.7 Upper Byte Enable (UB)

The Upper Byte Enable,  $\overline{\text{UB}}$ , gates the data on the Upper Byte Data Inputs/Outputs (DQ8-DQ15) to or from the upper part of the selected address during a write or read operation.

# 2.8 Lower Byte Enable (LB)

The Lower Byte Enable,  $\overline{LB}$ , gates the data on the Lower Byte Data Inputs/Outputs (DQ0-DQ7) to or from the lower part of the selected address during a write or read operation.

If both  $\overline{LB}$  and  $\overline{UB}$  are disabled (High), the device will disable the data bus from receiving or transmitting data. Although the device will seem to be deselected, it remains in an active mode as long as  $\overline{E}$  remains Low.

### 2.9 Clock Input (K)

The Clock, K, is an input signal to synchronize the memory to the microcontroller or system bus frequency during Synchronous Burst Read and Write operations. The Clock input signal increments the device internal address counter.

The addresses are latched on the rising edge of the Clock K, when  $\overline{L}$  is Low during Synchronous Bus operations.

Latency counts are defined from the first Clock rising edge after  $\overline{L}$  falling edge to the first data input latched or the first data output valid.

The Clock input is required during all synchronous operations and must be kept Low during asynchronous operations.

# 2.10 Configuration Register Enable (CR)

When this signal is driven High,  $V_{IH}$ , bus read or write operations access either the value of the Refresh Configuration Register (RCR) or the Bus Configuration Register (BCR) according to the value of A19.

# 2.11 Latch Enable ( $\overline{L}$ )

In Synchronous mode, addresses are latched on the rising edge of the Clock K when the Latch Enable input,  $\overline{L}$  is Low. In Asynchronous mode, addresses are latched on  $\overline{L}$  rising edge.

### 2.12 Wait (WAIT)

The WAIT output signal provides data-valid feedback during Synchronous Burst Read and Write operations. The signal is gated by  $\overline{E}$ . Driving  $\overline{E}$  High while WAIT is asserted may cause data corruption.

Once a read or write operation has been initiated, the WAIT signal goes active to indicate that the M69KB128AA device requires additional time before data can be transferred.

The WAIT signal also is used for arbitration when a Read or Write operation is launched while an on-chip refresh is in progress (see *Figure 6: Refresh Collision during Synchronous Read Operation in Variable Latency mode*).

Typically, the WAIT pin of the M69KB128AA can be connected to a shared WAIT signal used by the processor to coordinate transactions with multiple memories on the synchronous bus.

See Section 3: Power-up for details on the WAIT signal operation.

# 2.13 V<sub>CC</sub> Supply Voltage

The  $V_{CC}$  Supply Voltage is the core supply voltage.

# 2.14 V<sub>CCQ</sub> Supply Voltage

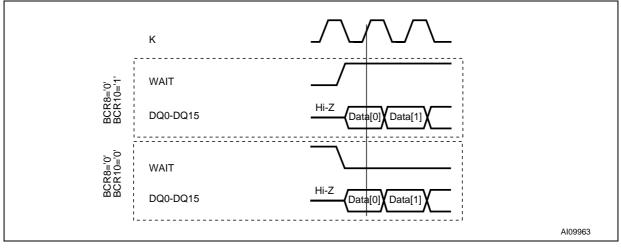

$V_{CCQ}$  provides the power supply for the I/O pins. This allows all Outputs to be powered independently from the core power supply,  $V_{CC}\!$

# 2.15 V<sub>SS</sub> Ground

The  $V_{\mbox{\scriptsize SS}}$  Ground is the reference for all voltage measurements.

# 2.16 V<sub>SSQ</sub> Ground

$V_{SSQ}$  ground is the reference for the input/output circuitry driven by  $V_{CCQ}.~V_{SSQ}$  must be connected to  $V_{SS}.$

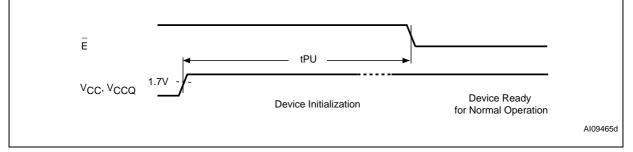

# 3 Power-up

To guarantee correct operation, a specific Power-Up sequence must be followed to initialize the M69KB128AA. Power must be applied simultaneously to  $V_{CC}$  and  $V_{CCQ}$ . Once  $V_{CC}$  and  $V_{CCQ}$  have reached a stable level (see *Figure 35: Deep Power-Down Entry and Exit AC Waveforms* and *Figure 34: Power-Up AC Waveforms*), the device will require  $t_{VCHEL}$  to complete its self-initialization process. During the initialization period, the  $\overline{E}$  signal must remain High. Once initialization has completed, the device is ready for normal operation.

Initialization will load the Bus Configuration Register (BCR) and the Refresh Configuration Register (RCR) with their default settings (see *Table 9: Bus Configuration Register Definition*, and *Table 11: Refresh Configuration Register Definition*).

# 4 Low-power modes

#### 4.1 Standby

When the device is in Standby, the current consumption is reduced to the level necessary to perform the memory array refresh operation. The device will enter Standby when a read or write operation is completed, depending on the operating mode (Asynchronous, NOR-Flash Synchronous or Full Synchronous).

For details on how to enter Standby, refer to *Table 3: Standard Asynchronous Operating* Modes, *Table 5: Asynchronous Write Operations (NOR-Flash Synchronous mode)* and *Table 6: Synchronous Read Operations (NOR-Flash Synchronous mode)*.

#### 4.2 Deep Power-Down

Deep Power-Down (DPD) is used by the system memory microcontroller to disable the PSRAM device when its storage capabilities are not needed. All refresh operations are then disabled.

For the device to enter Deep Power-Down, bit 4 of the RCR must be set to '0' and Chip Enable,  $\overline{E}$ , must go High, V<sub>IH</sub>. When the Deep Power-Down is enabled, the data stored in the device may be corrupted and BCR, RCR and DIDR content are saved.

To exit Deep Power-Down, the Chip Enable signal,  $\overline{E}$ , must be held Low,  $V_{IL}$ , for a minimum time of  $t_{EHEL(DP)}$ . Bit 4 of the RCR will be automatically set to '1'. Once the Deep Power-Down is exited, the device will be available for normal operations after  $t_{VCHEL}$  (time to perform an initialization sequence) During this delay, the current consumption will be higher than the specified Standby levels, but considerably lower than the active current. The content of the registers will be restored after Deep Power-Down.

For details on how to enter Deep Power-Down, refer to *Table 3: Standard Asynchronous Operating Modes, Table 5: Asynchronous Write Operations (NOR-Flash Synchronous mode)* and *Table 6: Synchronous Read Operations (NOR-Flash Synchronous mode)*.

### 4.3 Partial Array Self Refresh

The Partial Array Self Refresh (PASR) performs a limited refresh of part of the PSRAM array. This mechanism enables the device to reduce the Standby current by refreshing only the part of the memory array that contains essential data. Different refresh options can be defined by setting the RCR0 to RCR2 bits of the RCR:

- Full array

- One eighth of the array

- One half of the array

- One quarter of the array

- None of the array.

These memory areas can be located either at the top or bottom of the memory array.

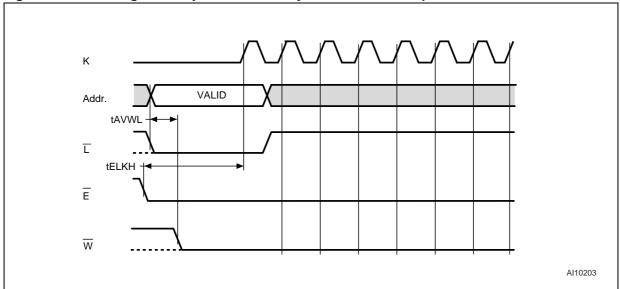

The WAIT signal is used for arbitration when a read/write operation is launched while an onchip refresh is in progress. If locations are addressed while they are undergoing refresh, the WAIT signal will be asserted for additional clock cycles, until the refresh has completed (see *Figure 6: Refresh Collision during Synchronous Read Operation in Variable Latency mode*). When the refresh operation is completed, the read or write operation will be allowed to continue normally.

# 5 Standard asynchronous operating modes

The M69KB128AA supports Asynchronous Read and Write modes (Random Read, Page Read, Asynchronous Write).

The device is put in Asynchronous mode by setting bit 15 (BCR15) of the BCR to '1'. The Page mode is controlled by the Refresh Configuration Register (bit RCR7).

During asynchronous operations, the WAIT signal should be ignored and the Clock input signal K should be held Low,  $V_{IL}$ .

Refer to *Table 3: Standard Asynchronous Operating Modes* for a detailed description of asynchronous operating modes.

#### 5.1 Asynchronous Read and Write modes

At Power-Up, the device defaults to Asynchronous Random Read mode (bit BCR15 set to '1'). This mode uses the industry standard control bus ( $\overline{E}$ ,  $\overline{G}$ ,  $\overline{W}$ ,  $\overline{LB}$ ,  $\overline{UB}$ ). Read operations are initiated by bringing  $\overline{E}$  and  $\overline{G}$  Low, V<sub>IL</sub>, while keeping  $\overline{W}$  High, V<sub>IH</sub>. Valid data will be gated through the output buffers after the specific access time t<sub>ELQV</sub> has elapsed.

Write operations occur when  $\overline{E}$  and  $\overline{W}$  are Low. During Asynchronous Random Write operations, the  $\overline{G}$  signal is 'don't care' and  $\overline{W}$  will override  $\overline{G}$ . The data to be written is latched on the rising edge of  $\overline{E}$ ,  $\overline{W}$ ,  $\overline{LB}$  or  $\overline{UB}$  (whichever occurs first). The write operation is terminated by de-asserting  $\overline{E}$ ,  $\overline{W}$ ,  $\overline{LB}$  or  $\overline{UB}$ .

The  $\overline{L}$  input can either be used to latch the address or kept Low, V<sub>IL</sub>, during the entire read/write operation.

See *Figure 14* and *Figure 15*, and *Table 17* for details on Asynchronous Read AC waveforms and characteristics and *Figure 18*, *Figure 19*, *Figure 20*, and *Figure 19* for details of Asynchronous Write AC waveforms and characteristics.

#### 5.2 Asynchronous Page Read mode

Asynchronous Page Read mode is enabled by setting RCR7 to '1'. The Latch Enable,  $\overline{L}$ , and the Chip enable  $\overline{E}$  must be held Low, V<sub>IL</sub> during Asynchronous Page Read operations.

A Page of data is internally read. A memory page may consist of 4, 8 or 16 Words. During a 4-Word page access, all the address bits except A0 to A1 should be fixed. During a 8-Word and 16-Word page access, all address bits are fixed except A0 to A2 and A0 to A3, respectively (see *Table 2: Page Mode Characteristics*).

The first read operation within the Page has the normal access time ( $t_{AVQV}$ ), subsequent reads within the same Page have much shorter access times ( $t_{AVQV1}$ ). If the Page changes then the normal, longer timings apply again.

The Page mode is not available for write operations.

See Figure 16 and Table 17 for details of the Asynchronous Page Read timing requirements.

| Table 2. Tage W |                   |                         |                     |

|-----------------|-------------------|-------------------------|---------------------|

| Page Size       | Page Read Address | Page Read Start Address | Page Read Direction |

| 4 Words         | A0-A1             | Don't Care              | Don't Care          |

| 8 Words         | A0-A2             | Don't Care              | Don't Care          |

| 16 Words        | A0-A3             | Don't Care              | Don't Care          |

Table 2.

Page Mode Characteristics

# 5.3 Configuration Registers Asynchronous Read and Write

Programming the registers (BCR and RCR) and reading the registers (BCR, RCR and DIDR) can be performed using the CR controlled method in standard Asynchronous mode.

| Asynchronous<br>Modes <sup>(1)</sup>                                   | Power                                           | Ē               | Ē               | w               | G               | UB              | LB              | WAIT            | CR                        | A19          | A18                        | A0-A17<br>A20-A22 | DQ0-<br>DQ7        | DQ8-<br>DQ15    |

|------------------------------------------------------------------------|-------------------------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|---------------------------|--------------|----------------------------|-------------------|--------------------|-----------------|

| Word Read                                                              |                                                 |                 |                 |                 | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IL</sub> |                 | V <sub>IL</sub>           |              | Val                        | lid               | Output<br>Valid    | Output<br>Valid |

| Lower Byte<br>Read                                                     |                                                 |                 |                 | $V_{\rm IH}$    | V <sub>IL</sub> | VIH             | V <sub>IL</sub> |                 | V <sub>IL</sub>           |              | Val                        | lid               | Output<br>Valid    | High-Z          |

| Upper Byte<br>Read                                                     |                                                 |                 |                 |                 | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> |                 | V <sub>IL</sub>           |              | Val                        | lid               | High-Z             | Output<br>Valid |

| Word Write                                                             |                                                 |                 |                 |                 | х               | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IL</sub> Val       |              | lid                        | Input<br>Valid    | Input<br>Valid     |                 |

| Lower Byte<br>Write                                                    | Active                                          | .,              |                 | V <sub>IL</sub> | х               | VIH             | V <sub>IL</sub> |                 | V <sub>IL</sub>           | Valid        |                            |                   | Input<br>Valid     | Invalid         |

| Upper Byte<br>Write                                                    | (I <sub>CC</sub> )                              | V <sub>IL</sub> | V <sub>IL</sub> |                 | х               | V <sub>IL</sub> | VIH             | Low-<br>Z       | V <sub>IL</sub>           | Valid        |                            | Invalid           | Input<br>Valid     |                 |

| Read<br>Configuration<br>Register<br>(CR Controlled<br>Method)         |                                                 |                 |                 | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IL</sub> |                 | V <sub>IH</sub>           | 10(E<br>X1(D | RCR)<br>BCR)<br>NDR)<br>2) | х                 | BC<br>RCR/I<br>Con | DIDR            |

| Program<br>Configuration<br>Register (CR<br>Controlled) <sup>(3)</sup> |                                                 |                 |                 | V <sub>IH</sub> | x               | x               | х               |                 | 00(RCR)<br>10(BCR)<br>(2) |              | BCR/<br>RCR<br>Data        | Higl              | n-Z                |                 |

| No Operation                                                           | Active<br>(I <sub>CC</sub> )                    |                 |                 | х               | х               | х               | х               |                 | V <sub>IL</sub>           | х            | х                          | х                 | Х                  |                 |

| Deep<br>Power-Down <sup>(4)</sup>                                      | Deep<br>Power-<br>Down X<br>(I <sub>CCPD)</sub> |                 | V <sub>IH</sub> | x               | x               | x               | х               | High-<br>Z      | x                         | x            | х                          | х                 | Higl               | n-Z             |

| Standby                                                                | Standby<br>(I <sub>PASR</sub> )                 |                 | V <sub>IH</sub> | х               | х               | х               | х               |                 | V <sub>IL</sub>           | х            | х                          | х                 | Higl               | n-Z             |

Table 3.

Standard Asynchronous Operating Modes

1. The Clock signal, K, must remain Low in asynchronous operating mode.

2. A18 and A19 are used to select the BCR, RCR or DIDR registers.

3. BCR and RCR only.

4. Bit 4 of the Refresh Configuration Register must be set to '0', bit 4 (BCR4) of the Bus Configuration Register must be set to '0', and E has to be maintained High, V<sub>IH</sub>, during Deep Power-Down mode.

# 6 Synchronous operating modes

The synchronous modes allow high-speed read and write operations synchronized with the clock. Refresh cycles are indicated to the host system by asserting the WAIT signal that, in turn, stalls the microcontroller.

The M69KB128AA supports two types of synchronous modes:

- NOR-Flash:- this mode greatly simplifies the interfacing with traditional burst-mode Flash memory microcontrollers.

- Full Synchronous: both read and write are performed in Synchronous mode.

All the options related to the synchronous modes can be configured through the Bus Configuration Register, BCR. In particular, the device is put in Synchronous mode, either NOR-Flash or Full Synchronous, by setting bit BCR15 of the Bus Configuration Register to '0'.

The device will automatically detect whether the NOR-Flash or the Full Synchronous mode is being used by monitoring the Clock, K, and the Latch Enable,  $\overline{L}$ , signals. If a rising edge of the Clock K is detected while  $\overline{L}$  is held Low,  $V_{IL}$  (active), the device operates in Full Synchronous mode.

#### 6.1 NOR-Flash Synchronous mode

In this mode, the device operates in synchronous mode for read operations, and in asynchronous mode for write operations.

Asynchronous write operations are performed at Word level, with  $\overline{LB}$  and  $\overline{UB}$  Low. The data is latched on  $\overline{E}$ ,  $\overline{W}$ ,  $\overline{LB}$ ,  $\overline{UB}$ , whichever occurs first. RCR and BCR registers can be programmed in NOR-Flash Asynchronous Write mode, using the CR controlled method (see Section 7.1: *Programming the Registers by the CR controlled method*). A Program Configuration Register operation can only be issued if the device is in idle state and no burst operations are in progress. NOR-Flash Asynchronous Write operations are described in *Table 5: Asynchronous Write Operations (NOR-Flash Synchronous mode*).

Synchronous read operations are also performed at Word level. They are controlled by the state of  $\overline{E}$ ,  $\overline{L}$ ,  $\overline{G}$ ,  $\overline{W}$ ,  $\overline{LB}$  and  $\overline{UB}$  signals when a rising edge of the clock signal, K, occurs. The initial Burst Read access latches the Burst start address. The number of Words to be output is controlled by bits 0 to 2 of the BCR. The first data will be output after a number of clock cycles, also called Latency. NOR-Flash Synchronous Burst Read operations are described in *Table 6:* Synchronous Read Operations (NOR-Flash Synchronous mode).

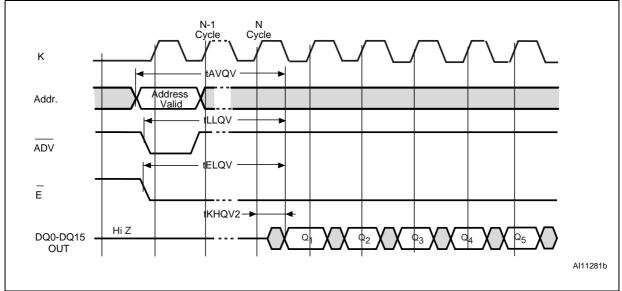

When a Burst Write operation is initiated or when switching from NOR-Flash mode to Full Synchronous mode, the delay from  $\overline{E}$  Low to Clock High, t<sub>ELKH</sub>, should not exceed 20ns. However, when it is not possible to meet these specifications, special care must be taken to keep addresses stable after driving the Write Enable signal,  $\overline{W}$ , Low.

Write operations are considered as Asynchronous operations until the device detects a valid clock edge and hence the address setup time of t<sub>AVWL</sub> must be satisfied (see *Figure 5: Switching from Asynchronous to Synchronous Write operation*).

#### 6.2 Full Synchronous mode

In Full Synchronous mode, the device performs read and write operations synchronously. Synchronous Read and Write operations are performed at Word level.

The initial Burst Read and Write access latches the Burst start address. The number of Words to be output or input during Synchronous Read and Write operations is controlled by bits 0 to 2 of the BCR.

During Burst Read and Write operations, the first data will be output after a number of clock cycles defined by the Latency value.

Programming the registers (BCR and RCR) and reading the registers (BCR, RCR and DIDR) can be performed using the CR controlled method in Full Synchronous mode.

Full Synchronous operations are described in Table 7: Full Synchronous mode.

#### 6.3 Synchronous Burst Read and Write

During Synchronous Burst Read or Write operations, addresses are latched on the rising edge of the Clock K when  $\overline{L}$  is Low and data are latched on the rising edge of K. The Write Enable,  $\overline{W}$ , signal indicates whether the operation is going to be a read ( $\overline{W}=V_{IH}$ ) or a write ( $\overline{W}=V_{IL}$ ).

The WAIT output will be asserted as soon as a Synchronous Burst operation is initiated and will be deasserted to indicate when data are to be transferred to (or from) the memory array.

The Burst Length is the number of Words to be output or input during a Synchronous Burst Read or Write operation. It can be configured as 4, 8, 16 or 32 Words or continuous through bit BCR0 to BCR2 or the Burst Configuration Register. The Latency defines the number of clock cycles between the beginning of a Burst Read operation and the first data output (counting from the first Clock edge where  $\overline{L}$  was detected Low) or between the beginning of a Burst Write operation and the first data input. The Latency can be set through bits BCR13 to BCR11 of the Bus Configuration Register (see *Table 4: Operating Frequency versus Latency*).

The latency can also be configured to fixed or variable by programming bit BCR14. By default, the Latency Type is set to variable.

Synchronous Read operations are performed in both fixed and variable latency mode while Synchronous Write operations are only performed with fixed latency.

See *Figure 24*, *Note 1*, and *Figure 30*, *Note 31*, for details on Synchronous Read and Write AC waveforms, respectively.

#### 6.3.1 Variable Latency

In Variable Latency mode, the latency programmed in the BCR is not guaranteed and is maintained only if there is no conflict with a refresh operation.

The Latency set in the BCR is applicable only for an initial burst read access, when no refresh request is pending. For a given latency value, the Variable Latency mode allows higher operating frequencies than the Fixed Latency mode (see *Table 4: Operating Frequency versus Latency* and *Figure 3: Latency Configuration (Variable Latency mode, no Refresh collision)*).

Burst Write operations are always performed at fixed latency, even if BCR14 is configured to Variable Latency (see Section 6.3.2: Fixed Latency).

Monitoring of the WAIT signal is recommended for reliable operation in this mode.

See *Figure 24*. and *Figure 31* for details on Synchronous Burst Read and Write AC waveforms in Variable Latency mode.

#### 6.3.2 Fixed Latency

The latency programmed in the BCR is the real latency. The number of clock cycles is calculated by taking into account the time necessary for a refresh operation and the time necessary for an initial Burst access. This limits the operating frequency for a given latency value (see *Table 4: Operating Frequency versus Latency* and *Figure 4: Latency Configuration (Fixed Latency mode)*).

It is recommended to use the Fixed Latency mode if the microcontroller cannot monitor the WAIT signal.

#### 6.3.3 Row Boundary crossing

The M69KB128AA features 128-Word rows. Row boundary crossings between adjacent rows may occur during Burst Read and Write operations. Row boundary crossings are not handled automatically by the PSRAM.

The microcontroller must stop the Burst operation at the row boundary and restart it at the beginning of the next row. Burst operations must be stopped by driving the Chip Enable signal,  $\overline{E}$ , High, after the WAIT signal falling edge.  $\overline{E}$  must transition:

- Before the third Clock cycle after the WAIT signal goes Low if BCR[8] = 0

- Before the fourth Clock cycle after WAIT signal goes Low if BCR[8] = 1.

Refer to *Figure 26* and *Figure 30* for details on how to manage row boundary crossings during burst operations.

### 6.4 Synchronous Burst Read Interrupt

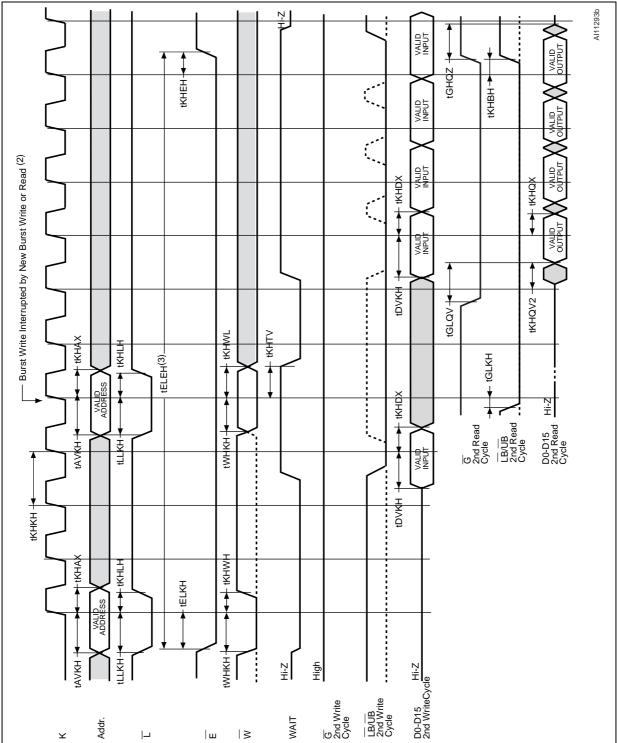

Ongoing Burst Read operations can be interrupted to start a new Burst cycle by either of the following means:

- Driving E High, V<sub>IH</sub>, and then Low, V<sub>IL</sub> on the next clock cycle (recommended). If necessary, refresh cycles will be added during the new Burst operation to schedule any outstanding refresh. If Variable Latency mode is set, additional wait cycles will be added if a refresh operation is scheduled during the Synchronous Burst Read Interrupt. WAIT monitoring is mandatory for proper system operation.

- Starting a new Synchronous Burst Read operation without toggling  $\overline{E}$ .

An ongoing Burst Read operation can be interrupted only after the first valid data is output. When a new Burst access starts, I/O signals immediately become high impedance.

# 6.5 Synchronous Burst Write Interrupt

Ongoing Burst Write operations can be interrupted to start a new Burst cycle by either of the following means:

- Driving E High, V<sub>IH</sub>, and then Low, V<sub>IL</sub> on the next clock cycle (recommended),

- Starting a new Synchronous Burst Write without toggling E. Considering that Burst Writes are always performed in Fixed Latency mode, refresh is never scheduled. A maximum Chip Enable, E, low time (t<sub>ELEH</sub>) must be respected for proper device operation.

An ongoing Burst Write can be interrupted only after the first data is input. When a new Burst access starts, I/O signals immediately become high impedance.

See Figure 27: Burst Read Interrupted by Burst Read or Write AC Waveforms and Figure 32: Burst Write Interrupted by Burst Write or Read AC Waveforms for details on Burst Read and Burst Write interrupt AC waveforms, respectively.

# 6.6 Synchronous Burst Read and Write Suspend

Synchronous Burst Read and Write operations can be suspended by halting the Clock K holding it either High or Low. The status of the I/O signals will depend on the status of Output enable input,  $\overline{G}$ . The device internal address counter is suspended and data outputs become high impedance  $t_{GHQZ}$  after the rising edge of the Output Enable signal,  $\overline{G}$ . It is prohibited to suspend the first data output at the beginning of a Synchronous Burst Read.

See Figure 25 for details on the Synchronous Burst Read and Write Suspend mechanisms.

During Synchronous Burst Read and Synchronous Burst Write Suspend operations, the WAIT output will be asserted. Bit BCR8 of the Bus Configuration Register is used to configure when the transition of the WAIT output signal between the asserted and the deasserted state occurs with respect to valid data available on the data bus.

| Latency              | Configured                      |        | ency<br>Cycles)            | Max Input Clock Frequency (MHz) |        |        |  |  |  |  |

|----------------------|---------------------------------|--------|----------------------------|---------------------------------|--------|--------|--|--|--|--|

| Mode                 | Latency<br>(Clock Cycles)       | Normal | lf<br>Refresh<br>Collision | 104 MHz                         | 80 MHz | 66 MHz |  |  |  |  |

| Variable             | 2 (3 clock cycles)              | 3      | 5                          | 66                              | 52     | 40     |  |  |  |  |

| Latency<br>BCR14 = 0 | 3 (4 clock cycles)<br>(default) | 4      | 7                          | 104                             | 80     | 66     |  |  |  |  |

| (Default)            | All Others                      | -      | -                          | -                               | -      | -      |  |  |  |  |

|                      | 2 (3 clock cycles)              | :      | 3                          | 33                              | 33     | 20     |  |  |  |  |

| Fixed                | 3 (4 clock cycles)<br>(default) |        | 4                          | 52                              | 52     | 33     |  |  |  |  |

| Latency              | 4 (5 clock cycles)              | ł      | 5                          | 66                              | 66     | 40     |  |  |  |  |

| BCR14 = 1            | 5 (6 clock cycles)              | (      | 6                          | 75                              | 75     | 52     |  |  |  |  |

|                      | 6 (7 clock cycles)              | -      | 7                          | 104                             | 80     | 66     |  |  |  |  |

|                      | All Others                      |        | -                          | -                               | -      | -      |  |  |  |  |

Table 4.

Operating Frequency versus Latency

#### Table 5. Asynchronous Write Operations (NOR-Flash Synchronous mode)

| Asynchronous<br>Operations                                             | Power                                     | к               | Ē               | Ē               | w               | G               | UB,<br>LB | WAIT      | CR              | A19                | A18 | A0-A22              | DQ0-DQ15    |

|------------------------------------------------------------------------|-------------------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------|-----------|-----------------|--------------------|-----|---------------------|-------------|

| Word Write                                                             |                                           |                 | V <sub>IL</sub> | $V_{\text{IL}}$ | V <sub>IL</sub> | Х               | $V_{IL}$  |           | $V_{\text{IL}}$ |                    | Val | id                  | Input Valid |

| Program<br>Configuration<br>Register (CR<br>Controlled) <sup>(1)</sup> | Active (I <sub>CC</sub> )                 |                 | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | х         | Low-<br>Z | V <sub>IH</sub> | 00(RCR)<br>10(BCR) |     | RCR/<br>BCR<br>Data | High-Z      |

| No Operation                                                           | Active (I <sub>CC</sub> )                 | $V_{\text{IL}}$ | $V_{\text{IH}}$ | Х               | Х               | Х               | Х         |           | $V_{\text{IL}}$ |                    | Х   |                     | Х           |

| Standby                                                                | Standby<br>(I <sub>PASR</sub> )           |                 | х               | V <sub>IH</sub> | х               | х               | х         | High-     | V <sub>IL</sub> |                    | Х   |                     | High-Z      |

| Deep<br>Power-Down                                                     | Deep<br>Power-Down<br>(I <sub>CCPD)</sub> |                 | х               | V <sub>IH</sub> | х               | х               | х         | Z         | х               |                    | х   |                     | High-Z      |

1. BCR and RCR only.

| Table 0. Synchronous Read Operations (NOR-Hash Synchronous mode) |                                               |                 |                 |                 |                 |                 |                                |            |                 |                                  |       |                                 |                 |

|------------------------------------------------------------------|-----------------------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|--------------------------------|------------|-----------------|----------------------------------|-------|---------------------------------|-----------------|

| Synchronous<br>Operations <sup>(1)</sup>                         | Power                                         | к               | Ē               | Ē               | w               | G               | LB,<br>UB                      | WAIT       | CR              | A19                              | A18   | A0-<br>A22 <sup>(2)</sup>       | DQ15-<br>DQ0    |

| Initial Burst<br>Read                                            |                                               | =               | V <sub>IL</sub> | V <sub>IL</sub> | VIH             | х               | V <sub>IL</sub>                |            | V <sub>IL</sub> | Valid                            | Valid | Valid                           | Output<br>Valid |

| Subsequent<br>Burst Read                                         |                                               | =               | V <sub>IL</sub> | VIH             | х               | х               | V <sub>IL</sub> <sup>(3)</sup> |            | V <sub>IL</sub> | x                                |       |                                 | Output<br>Valid |

| Read<br>Configuration<br>Register<br>(CR Controlled<br>Method)   | Active (I <sub>CC</sub> )                     | =               | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IL</sub>                | Low-Z      | V <sub>IH</sub> | 00(RCR)<br>10(BCR) X<br>X1(DIDR) |       | RCR/<br>BCR/<br>DIDR<br>Content |                 |

| No Operation                                                     | Active (I <sub>CC</sub> )                     | V <sub>IL</sub> | V <sub>IL</sub> | Х               | Х               | х               | Х                              |            | V <sub>IL</sub> |                                  | Х     |                                 | Х               |

| Standby                                                          | Standby<br>(I <sub>PASR</sub> )               | V <sub>IL</sub> | V <sub>IH</sub> | х               | х               | х               | х                              |            | V <sub>IL</sub> | х                                |       |                                 | High-Z          |

| Deep<br>Power-Down                                               | Deep<br>Power-<br>Down<br>(I <sub>CCPD)</sub> | V <sub>IL</sub> | V <sub>IH</sub> | х               | x               | x               | х                              | High-<br>Z | x               | Х                                |       | High-Z                          |                 |

Table 6.

Synchronous Read Operations (NOR-Flash Synchronous mode)

1. Burst Read Interrupt, Suspend and Terminate are described in dedicated paragraph of the Section 6: Synchronous operating modes.

2. Except A18 and A19.

The above table shows the device behavior if both LB and UB are asserted, V<sub>IL</sub>. If either LB or UB is High, V<sub>IH</sub>, only one Byte will be input or output, according to the status of W.

| Synchronous<br>Mode <sup>(1)</sup>                                | Power                                         | к               | Ē               | Ē               | w               | G               | LB,<br>UB                      | WAIT   | CR              | A19   | A18                   | A0-<br>A22 <sup>(2)</sup> | DQ15-<br>DQ0                    |

|-------------------------------------------------------------------|-----------------------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|--------------------------------|--------|-----------------|-------|-----------------------|---------------------------|---------------------------------|

| Initial Burst<br>Read                                             |                                               | =               | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | х               | V <sub>IL</sub>                |        | V <sub>IL</sub> | Valid | Valid                 | Valid                     | Х                               |

| Subsequent<br>Burst Read                                          |                                               | =               | V <sub>IL</sub> | V <sub>IH</sub> | х               | V <sub>IL</sub> | V <sub>IL</sub> <sup>(3)</sup> |        | V <sub>IL</sub> | х     | )                     | X                         | Output<br>Valid                 |

| Initial Burst<br>Write                                            |                                               | =               | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | х                              |        | V <sub>IL</sub> | Valid | Valid                 | Valid                     | Input<br>Valid                  |

| Subsequent<br>Burst Write                                         |                                               | =               | V <sub>IL</sub> | V <sub>IH</sub> | х               | V <sub>IH</sub> | V <sub>IL</sub> <sup>(2)</sup> |        | х               | х     | х                     | х                         | Input<br>Valid                  |

| Program<br>Configuration<br>Register<br>(CR<br>Controlled)        | Active<br>(I <sub>CC</sub> )                  | =               | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | х                              | Low-Z  | V <sub>IH</sub> |       | RCR)<br>BCR)          | RCR/<br>BCR<br>Data       | Х                               |

| Read<br>Configuration<br>Register<br>(CR<br>Controlled<br>Method) |                                               | =               | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IL</sub>                |        | V <sub>IH</sub> | 10(E  | RCR)<br>BCR)<br>DIDR) | x                         | RCR/<br>BCR/<br>DIDR<br>Content |

| No Operation                                                      | Active<br>(I <sub>CC</sub> )                  | V <sub>IL</sub> | V <sub>IL</sub> | х               | х               | х               | х                              |        | V <sub>IL</sub> |       | х                     |                           | х                               |

| Standby                                                           | Standby<br>(I <sub>PASR</sub> )               | V <sub>IL</sub> | VIH             | х               | х               | х               | х                              |        | V <sub>IL</sub> |       | х                     |                           | High-Z                          |

| Deep<br>Power-Down                                                | Deep<br>Power-<br>Down<br>(I <sub>CCPD)</sub> | V <sub>IL</sub> | V <sub>IH</sub> | х               | х               | х               | x                              | High-Z | х               |       | х                     |                           | High-Z                          |

Table 7. Full Synchronous mode

1. Burst Read Interrupt, Suspend, Terminate and Burst Write Interrupt, Suspend and Terminate are described in dedicated paragraph of the Section 6: Synchronous operating modes.

2. Except A18 and A19.

3. The above table shows the device behavior if both  $\overline{LB}$  and  $\overline{UB}$  are asserted,  $V_{IL}$ . If either  $\overline{LB}$  or  $\overline{UB}$  is High,  $V_{IH}$ , only one Byte will be input or output, according to the status of  $\overline{W}$ .

Figure 3. Latency Configuration (Variable Latency mode, no Refresh collision)

1. See *Table 21: Synchronous Burst Read AC Characteristics* for details on the synchronous read AC Characteristics shown in the above waveforms.

57

Figure 5. Switching from Asynchronous to Synchronous Write operation

Additional Wait states are inserted to allow Refresh completion. The latency is set to 3 clock cycles (BCR13-BCR11 = 010). The WAIT must be active Low, V<sub>IL</sub>, (BCR10 = 0) and asserted during delay (BCR8= 0).

# 7 Configuration registers

The M69KB128AA features three registers:

- The Bus Configuration Register (BCR)

- The Refresh Configuration Register (RCR)

- The Device ID Register (DIDR).

BCR and RCR are user-programmable registers that define the device operating mode. They are automatically loaded with default settings during Power-Up, and selected by address bits A18 and A19 (see *Table 8: Register Selection*).

DIDR is a read-only register that contains information about the device identification. It is selected by setting address bit A18 to '1' with A19 'don't care' (see *Table 8: Register Selection*).

The configuration registers (only BCR and RCR) can be programmed and read using two methods:

- The CR Controlled Method (or Hardware Method)

- The Software Method.

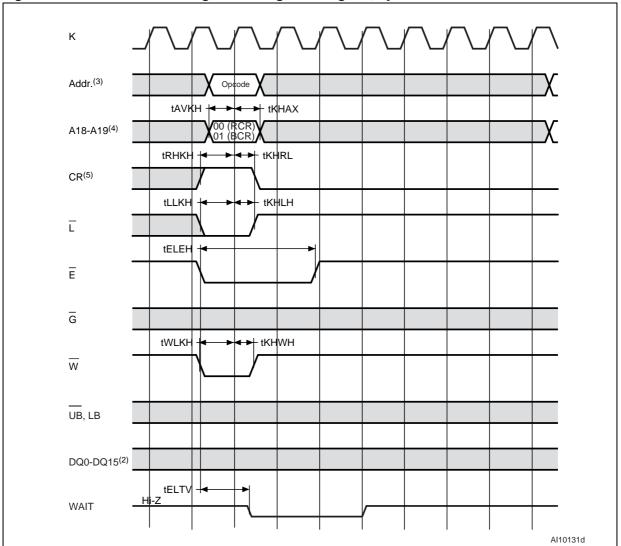

# 7.1 Programming the Registers by the CR controlled method

#### 7.1.1 Read Configuration Register

The content of a register is read by issuing a read operation with Configuration Register Enable signal, CR, High, V<sub>IH</sub>. Address bits A18 and A19 select the register to be read (see *Table 8: Register Selection*). The value contained in the register is then available on data bits DQ0 to DQ15.

The BCR, RCR and DIDR can be read either in normal asynchronous or synchronous mode.

The CR pin has to be driven high prior to any access.

See *Table 6* and *Table 7* for a detailed description of Configuration register Read by the CR Controlled methods and *Figure 17* and *Figure 28*, CR Controlled Configuration Register Read waveforms in asynchronous and synchronous mode.

#### 7.1.2 Program Configuration Register

BCR and RCR registers can be programmed by issuing a bus write operation, in asynchronous or synchronous mode (NOR-Flash or Full Synchronous), with Configuration Register Enable signal, CR, High, V<sub>IH</sub>. Address bits A18 and A19 allow to select between BCR and RCR (see *Table 8: Register Selection*).

In synchronous mode, the values placed on address lines A0 to A15 are latched on the rising edge of  $\overline{L}$ ,  $\overline{E}$ , or  $\overline{W}$ , whichever occurs first.

In asynchronous mode, a register is programmed by toggling  $\overline{L}$  signal.

LB and UB are 'don't care'. The CR pin has to be driven high prior to any access.

Refer to *Table 5* and *Table 7* for a detailed description of Configuration Register Program by the CR Controlled method and to *Figure 22* and *Figure 33*, showing CR controlled Configuration Register Program waveforms in asynchronous and synchronous mode.

| Register | Read or Write Operation | A18 | A19 |

|----------|-------------------------|-----|-----|

| RCR      | Read/Write              | 0   | 0   |

| BCR      | Read/Write              | 0   | 1   |

| DIDR     | Read-Only               | 1   | х   |

| Table 8. | Register | Selection |

|----------|----------|-----------|

|----------|----------|-----------|

# 7.2 Programming and Reading the Registers by the software method

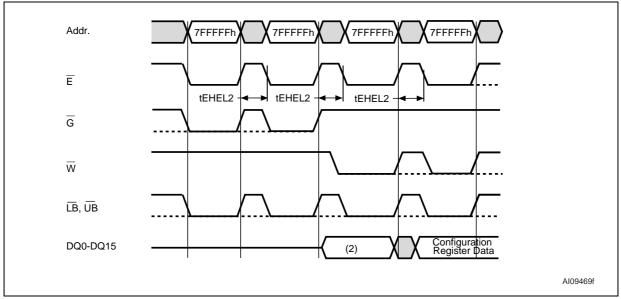

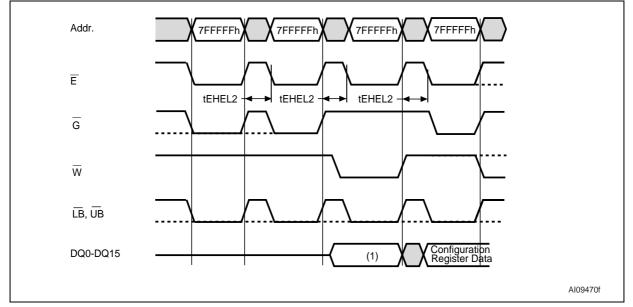

All registers (BCR, RCR, DIDR) can be read by issuing a Read Configuration Register sequence (see *Figure 8: Read Configuration Register (Software Method)*.

BCR and RCR can be programmed by issuing a Set Configuration Register sequence (see *Figure 7: Set Configuration Register (Software Method)*.

The timings will be identical to those described in *Table 17: Asynchronous Read AC Characteristics*. The Configuration Register Enable input, CR, is 'don't care'.

Read Configuration Register and Set Configuration Register sequences both require 4 read or write cycles. These cycles will be executed in asynchronous mode, whatever the device operating mode:

- 1. 2 bus read and one bus write cycles to a unique address location, 7FFFFFh, indicate that the next operation will read or write to a configuration register. The data written during the third cycle must be '0000h' to access the RCR, '0001h' to access the BCR and '0002h' to access the DIDR during the next cycle.

- 2. The fourth cycle reads from or writes to the configuration register.

The timings for programming and reading the registers by the software method are identical to the asynchronous write and read timings.

Figure 7. Set Configuration Register (Software Method)

1. Only the Bus Configuration Register (BCR) and the Refresh Configuration Register (RCR) can be modified.

- 2. To program the BCR or the RCR on last bus write cycle, DQ0-DQ15 must be set to '0001h' and '0000' respectively.

- 3. The highest order address location is not modified during this operation.

- 4. The control signal  $\overline{E}$  must be toggled as shown in the above figure.

1. To read the BCR, RCR or DIDR on last bus read cycle, DQ0-DQ15 must be set to '0001h', '0000' and '0002' respectively.

- 2. The highest order address location is not modified during this operation.

- 3. The control signal  $\overline{E}$  must be toggled as shown in the above figure.

### 7.3 Bus Configuration Register

The Bus Configuration Register (BCR) defines how the PSRAM interacts with the system memory bus. All the device operating modes are configured through the BCR, except the Page mode which is configured through the RCR.

Refer to *Table 9* for the description of the Bus Configuration Register Bits.

#### 7.3.1 Operating Mode Bit (BCR15)

The Operating Mode bit allows the Synchronous mode or the Asynchronous mode (default setting) to be selected. Selecting the Synchronous mode will allow the device to operate either in NOR Flash mode or in full Synchronous Burst mode.

The device will automatically detect that the NOR Flash mode is being used by monitoring a rising edge of the Clock signal, K, when  $\overline{L}$  is Low. If this should not be the case, the device operates in full Synchronous mode.

#### 7.3.2 Latency Type (BCR14)

The Latency Type bit is used to configure the latency type. When the Latency Type bit is set to '0', the device operates in variable latency mode (only available for Synchronous Read mode). When it is '1', the fixed latency mode is selected and the latency is defined by the values of bits BCR13 to BCR11.

Refer to Table 3 and Table 4 for examples of fixed and variable latency configuration.

#### 7.3.3 Latency Counter Bits (BCR13-BCR11)

The Latency Counter bits are used to set the number of clock cycles between the beginning of a read or write operation and the first data output or input.

The Latency Counter bits can only assume the values shown in *Table 9: Bus Configuration Register Definition* (see also *Figure 3* and *Figure 4*).

#### 7.3.4 WAIT Polarity Bit (BCR10)

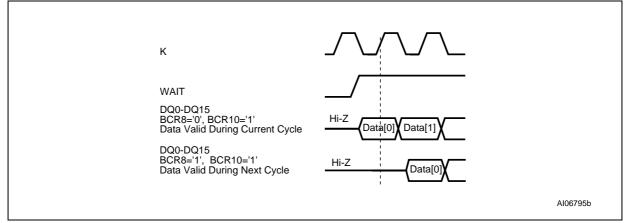

The WAIT Polarity bit indicates whether the WAIT output signal is active High or Low. As a consequence, it also determines whether the WAIT signal requires a pull-up or pull-down resistor to maintain the de-asserted state (see *Figure 10: WAIT Polarity*).

By default, the WAIT output signal is active High.

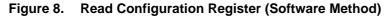

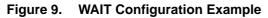

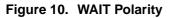

#### 7.3.5 WAIT Configuration Bit (BCR8)

The system memory microcontroller uses the WAIT signal to control data transfer during Synchronous Burst Read and Write operations.

The WAIT Configuration bit is used to determine when the transition of the WAIT output signal between the asserted and the deasserted state occurs with respect to valid data available on the data bus. When the Wait Configuration bit is set to '0', data is valid or invalid on the first Clock rising edge immediately after the WAIT signal transition to the deasserted or asserted state. When the Wait Configuration bit is set to '1' (default settings), the WAIT signal transition occurs one clock cycle prior to the data bus going valid or invalid.

See Figure 9: WAIT Configuration Example for an example of WAIT configuration.

#### 7.3.6 Driver Strength Bits (BCR5-BCR4)

The Driver Strength bits allow to set the output drive strength to adjust to different data bus loading. Normal driver strength (full drive) and reduced driver strength (half drive and a quarter drive) are available.

By default, outputs are configured at 'half drive" strength.

#### 7.3.7 Burst Wrap Bit (BCR3)

Burst Read operations can be confined inside the 4, 8, 16 or 32 Word boundary (wrap) or allowed to step across the boundary (no wrap). The Burst Wrap bit is used to select between 'wrap' and 'no wrap'. If the Burst Wrap bit is set to '1' (no wrap), the device outputs data sequentially regardless of burst boundaries. When Continuous Burst operation is selected, the internal address switches to 000000h if the read address passes the last address. By default, Burst wrap is disabled (see also *Table 10: Burst Type Definition*).

#### 7.3.8 Burst Length Bits (BCR2-BCR0)

The Burst Length bits set the number of Words to be output or input during a Synchronous Burst Read or Write operation. They can be set for 4 Words, 8 Words, 16 Words, 32 Words or Continuous Burst (default settings), where all the Words are output or input sequentially regardless of address boundaries (see also *Table 10: Burst Type Definition*).

| Address<br>Bits | Bus<br>Configuration<br>Register Bits | Name                    | Value               | Description                                                                    |  |  |  |

|-----------------|---------------------------------------|-------------------------|---------------------|--------------------------------------------------------------------------------|--|--|--|

| A15             | BCR15                                 | Operating Mode          | 0                   | Synchronous Mode (NOR Flash or Full<br>Synchronous Mode)                       |  |  |  |

|                 |                                       | Bit                     | 1                   | Asynchronous Mode (Default)                                                    |  |  |  |

|                 | 00044                                 | Later av Tra            | 0                   | Variable Latency (Default)                                                     |  |  |  |

| A14             | BCR14                                 | Latency Type            | 1                   | Fixed Latency                                                                  |  |  |  |

|                 |                                       |                         | 010                 | 3 Clock Cycles                                                                 |  |  |  |

|                 |                                       |                         | 011                 | 4 Clock Cycles (Default)                                                       |  |  |  |

|                 | BCR13-                                | Latency Counter         | 100                 | 5 Clock Cycles                                                                 |  |  |  |

| A13-A11         | BCR11                                 | Bits                    | 101                 | 6 Clock Cycles                                                                 |  |  |  |

|                 |                                       |                         | 110                 | 7 Clock Cycles                                                                 |  |  |  |

|                 |                                       |                         | Other Configuration | ons Reserved <sup>(1)</sup>                                                    |  |  |  |

|                 |                                       |                         | 0                   | WAIT Active Low                                                                |  |  |  |

| A10             | BCR10                                 | WAIT Polarity Bit       | 1                   | WAIT Active High (default).See <i>Figure 10: WAIT Polarity</i> .               |  |  |  |

| A9              | -                                     | -                       | Must be set to '0'  | Reserved <sup>(1)</sup>                                                        |  |  |  |

| 4.0             | DODA                                  | Wait                    | 0                   | WAIT Asserted During Delay (see <i>Figure 9: WAIT Configuration Example</i> ). |  |  |  |

| A8              | BCR8                                  | Configuration Bit       | 1                   | WAIT Asserted One Clock Cycle Before Delay (Default)                           |  |  |  |

| A7-A6           | -                                     | -                       | Must be set to '0'  | Reserved <sup>(1)</sup>                                                        |  |  |  |

|                 |                                       | Driver Strength<br>Bits | 00                  | Full Drive                                                                     |  |  |  |

|                 | BCR5-BCR4                             |                         | 01                  | 1/2 Drive (Default)                                                            |  |  |  |

| A5-A4           |                                       |                         | 10                  | 1/4 Drive                                                                      |  |  |  |

|                 |                                       |                         | 11                  | Reserved <sup>(1)</sup>                                                        |  |  |  |

|                 |                                       |                         | 0                   | Wrap                                                                           |  |  |  |

| A3              | BCR3                                  | Burst Wrap Bit          | 1                   | No Wrap (Default)                                                              |  |  |  |

|                 | BCR2-BCR0                             | Burst Length Bit        | 001                 | 4 Words                                                                        |  |  |  |

|                 |                                       |                         | 010                 | 8 Words                                                                        |  |  |  |

|                 |                                       |                         | 011                 | 16 Words                                                                       |  |  |  |

| A2-A0           |                                       |                         | 100                 | 32 Words                                                                       |  |  |  |

|                 |                                       |                         | 111                 | Continuous Burst (default)                                                     |  |  |  |

|                 |                                       |                         |                     | Other Configurations Reserved <sup>(1)</sup>                                   |  |  |  |

#### Table 9. Bus Configuration Register Definition

1. Programming the BCR with reserved value will force the device to use the default register settings.

|                 |              | 4 Words                            |                                           |                                            |                                            |                                    |

|-----------------|--------------|------------------------------------|-------------------------------------------|--------------------------------------------|--------------------------------------------|------------------------------------|

| Mode            | Start<br>Add | (Sequential)<br>BCR2-<br>BCR0=001b | 8 Words<br>(Sequential)<br>BCR2-BCR0=010b | 16 Words<br>(Sequential)<br>BCR2-BCR0=011b | 32 Words<br>(Sequential)<br>BCR2-BCR0=100b | Continuous Burst<br>BCR2-BCR0=111b |

|                 | 0            | 0-1-2-3                            | 0-1-2-3-4-5-6-7                           | 0-1-2-314-15                               | 0-1-2-330-31                               | 0-1-2-3511                         |

|                 | 1            | 1-2-3-0                            | 1-2-3-4-5-6-7-0                           | 1-2-3-414-15-0                             | 1-2-330-31-0                               | 1-2-3-4510-511-                    |

|                 | 2            | 2-3-0-1                            | 2-3-4-5-6-7-0-1                           | 2-3-4-515-0-1                              | 2-3-431-0-1                                | 2-3-4-5-6511-                      |

|                 | 3            | 3-0-1-2                            | 3-4-5-6-7-0-1-2                           | 3-4-515-0-1-2                              | 3-4-531-0-1-2                              | 3-4-5511-                          |

|                 | 4            |                                    | 4-5-6-7-0-1-2-3                           | 4-515-0-1-2-3                              | 4-5-631-0-1-2-3                            | 4-5511-                            |

| 0,)             | 5            |                                    | 5-6-7-0-1-2-3-4                           | 5-6-715-0-14                               | 5-6-731-0-14                               | 5-6-7511-                          |

| R3=,            | 6            |                                    | 6-7-0-1-2-3-4-5                           | 6-7-815-0-15                               | 6-7-831-0-15                               | 6-7-8511-                          |

| (BCI            | 7            |                                    | 7-0-1-2-3-4-5-6                           | 7-8-915-0-16                               | 7-8-931-0-16                               | 7-8-9511-                          |

| Wrap (BCR3='0') |              |                                    |                                           |                                            |                                            |                                    |

| \$              | 14           |                                    |                                           | 14-15-0-1-213                              | 14-1531-013                                | 14511-                             |

|                 | 15           |                                    |                                           | 15-0-1-214                                 | 15-0-131-0<br>14                           | 15511-                             |

|                 |              |                                    |                                           |                                            |                                            |                                    |

|                 | 30           |                                    |                                           |                                            | 30-31-028-29                               | 30511-                             |

|                 | 31           |                                    |                                           |                                            | 31-0-129-30                                | 31511-                             |

|                 | 0            | 0-1-2-3                            | 0-1-2-3-4-5-6-7                           | 0-1-2-314-15                               | 0-1-2-330-31                               | 0-1-2-3511                         |

|                 | 1            | 1-2-3-4                            | 1-2-3-4-5-6-7-8                           | 1-2-315-16                                 | 1-2-3-432                                  | 1-2-3-4512-                        |

|                 | 2            | 2-3-4-5                            | 2-3-4-5-6-7-8-9                           | 2-3-417                                    | 2-3-433                                    | 2-3-4-5513-                        |